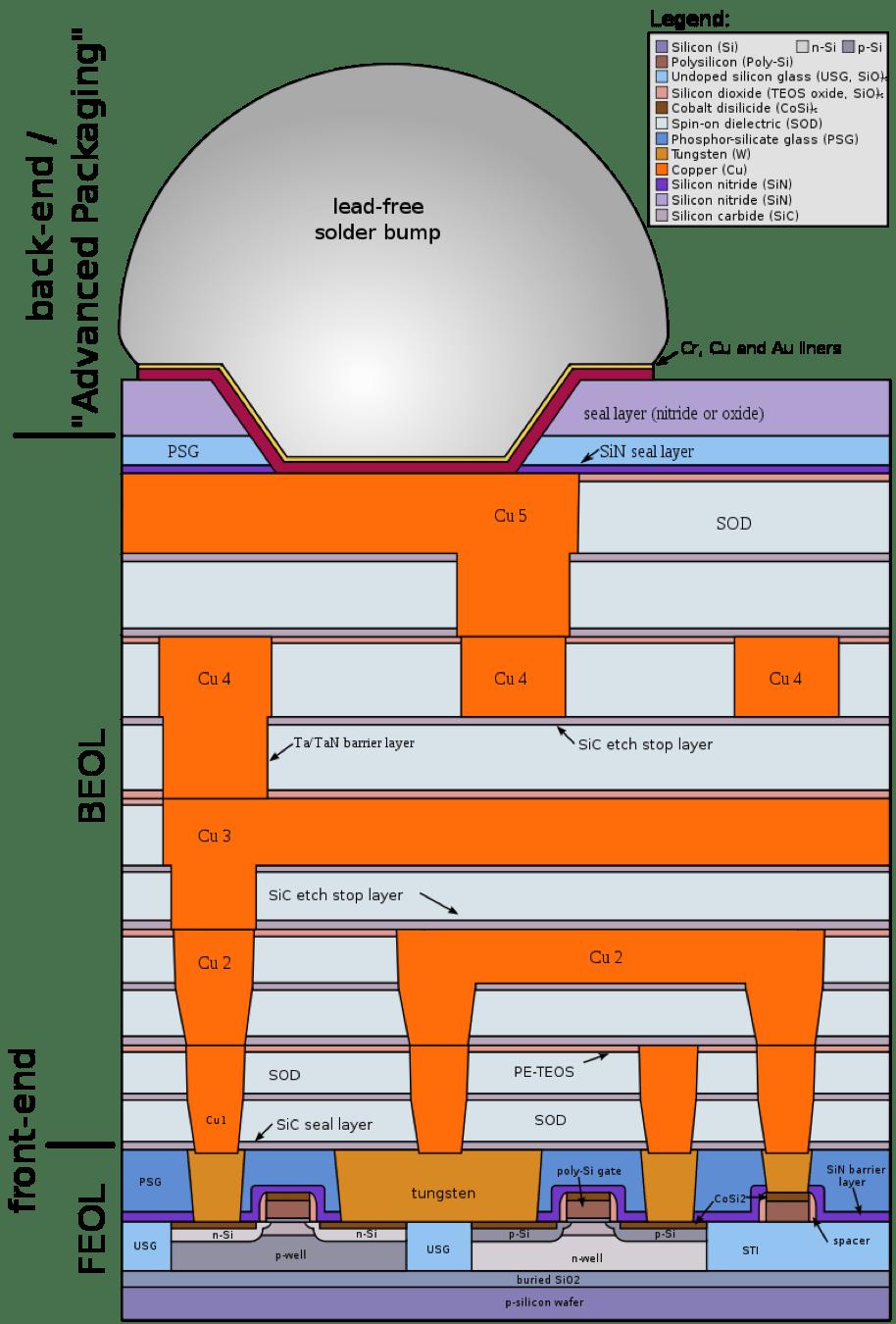

La escala de transistores está alcanzando un punto de inflexión a los 3 nm, donde los fets de la nanoshois probablemente reemplazarán a Finfets para cumplir con el rendimiento, la potencia, el área y los objetivos de costo (PPAC).Un cambio arquitectónico significativo se está evaluando de manera similar para las interconexiones de cobre a 2 nm, un movimiento que reconfiguraría la forma en que se entrega la potencia a los transistores.

Este enfoque se basa en los llamados rieles de energía enterrados (BPRS) y la distribución de energía trasera, dejando las interconexiones del lado delantera para transportar señales.Intel anunció que utilizará su estructura PowerVia en su generación de 20Å (equivalente de 2 nm), y otros fabricantes de chips están evaluando esquemas similares.

Es probable que los fabricantes de chips reemplacen el cobre en algunos niveles con rutenio o molibdeno tan pronto como el nodo de 2 nm.Otros cambios más modestos extenderán las interconexiones de damasceno de cobre utilizando baja resistencia a través de procesos, revestimientos alternativos y completamente alineados a través de enfoques.

Gran parte de la optimización ocurre alrededor de los enlaces débiles de la cadena: el contacto (metal 0), el metal 1 y los vías, donde los retrasos de RC tienen más probabilidades de frenar el chip.."Para el relleno, el relleno, la deposición conforme de la barrera, las semillas y el metal puede ser suplantado por una deposición sin barrera y un relleno de fondo de cobalto, y tal vez incluso Ruthenium", dijo Ajit Paranjpe, CTO de Veeco.

Los desafíos de interconexión comienzan en la litografía, donde el EUV se emplea en el proceso de 5 nm, contribuyendo significativamente al costo.

EUV and BEOL patterning

Only a handful of mask levels require EUV lithography at the 7nm node, but this changes to between 15 and 18 levels at 5nm (about 30nm metal pitch).En la litografía, una preocupación creciente son los errores de colocación de bordes (EPES) debido a características imprecisas alineadas.Robert Socha, un becario de ASML, enfatizó la necesidad de controlar y reducir los contribuyentes a las EPES en el nodo de 5 nm.Un contribuyente crítico son los errores de superposición, con un presupuesto de superposición de solo 2.5 nm (5 átomos de silicio de ancho) en el nodo de 5 nm.

"Hemos visto el elemento superpuesto del presupuesto de EPE reduciendo el más rápido con una mayor variación dentro del campo", dijo Andrew Cross, director de soluciones de control de procesos en KLA."Esto conduce a un mayor muestreo de superposición óptica, técnicas mejoradas de medición de superposición y el uso de mediciones de superposición basadas en SEM después de resistir el desarrollo y después del grabado, lo que requiere sinergia entre las herramientas ópticas y basadas en el viga electrónica."

Via optimization

A key strategy in extending copper technology involves eliminating the barrier metal, TaN, at the copper via bottom.Una forma en que esto se puede lograr es depositando una película de monocapa autoensamblada (SAM) selectivamente, depositando el bronceado por deposición de la capa atómica (ALD) a lo largo de las paredes laterales y finalmente eliminando el SAM y relleno de cobre.En IITC, Tel describió dicho proceso utilizando la integración dual de damasceno [1], y comparando dos monocapas autoensambladas (A y B).Después de la barrera tostada Ald, los SAM se evaporaron, seguido de deposición de electrodos de cobre (ELD) en Via (ver Higoura 1).Después de la pregrama, un revestimiento de Rutenio fue depositado por CVD en las paredes laterales de la trinchera, seguido de un relleno de PVD ionizado por cobre.Con Sam B, los resultados no mostraron TA (EDX) en la parte inferior.Un aspecto clave de cualquier SAM es que puede soportar la temperatura del proceso de ALD, que es de alrededor de 350 ° C.

Los fabricantes de chips buscan cada vez más los procesos SAM, ya sea por ECV o spin-coat, como crítico para reducir la resistencia general y extender los procesos de damasceno de cobre al nodo de 2 NM.

Otra estrategia que reduce el volumen de Barrera Metal (Tan) en el fondo Via implica una transición de PVD Tan a Ald Tan, que es más conforme y da como resultado una película más delgada y continua.Se espera que Ald Tan esté ampliamente implementado en el nodo de 5 nm, tal vez con los procesos SAM.

Higo.1: En este proceso de monocapa (SAM) autoensamblada, una película enmascara la parte inferior durante la barrera y la semilla de cobre.Luego se elimina el SAM por vaporización a 325 ° C, seguido de un relleno de cobre.Fuente: Tel/IITC

Fully aligned vias, selective deposition

The idea behind fully aligned vias (FAVs) is to reduce the impact of edge placement errors between vias and lines, which lead to device failures and long-term reliability issues.Desde el nodo de 32 nm, los fabricantes de chips han estado empleando métodos autoalineados utilizando máscaras duras de estaño para alinear las interconexiones al nivel inferior.En VIA completamente alineados, el Via a continuación y por encima está registrado.Hay dos métodos para lograr favoritos, grabando un poco de cobre de las líneas a continuación y luego al patrón y depositando el VIA, o depositando una película dieléctrica selectivamente en el dieléctrico bajo, seguido por el patrón.

Los ingenieros de IBM y LAM Research presentaron un enfoque totalmente alineado utiliza deposición dieléctrica selectiva en un proceso general simplificado [2].Según el grupo, la integración FAV puede permitir una resistencia 70% menor y un aumento del 30% en el área de contacto mientras se mantiene la confiabilidad de via a línea (ver Higoura 2).Utilizando estructuras de prueba de 32 nm-Pitch de cobre y dieléctrico bajo (SICOH), el equipo usó una química húmeda para recordar el cobre, el revestimiento y la barrera.

“[The recess etch], when combined with an etch-selective dielectric cap, acts as a via guiding pattern, mitigating overlay and critical dimension (CD) induced edge placement errors," according to IBM.La CVD depositó una película selectiva de óxido de aluminio en el bajo K y actúa como una parada de grabado parcial.La clave del éxito del proceso es una alta selectividad con sobrecrecimiento lateral limitado de la película dieléctrica, y sin disminución o variación de resistencia en comparación con su proceso FAV estándar.IBM declaró que una ventaja adicional es la relación de aspecto más baja de las líneas metálicas (porque el receso es poco profundo), que facilita el llenado de cobre.

En este momento, no está claro cómo se volverá los enfoques de los enfoques totalmente alineados. “The question is in what form — at what levels and at what pitch will (fully aligned vias) be required?" asks Zsolt Tokei, an Imec fellow.Señaló que si bien los enfoques de deposición selectiva y grabado de receso tienen sus pros y contras, el tema clave es la defectividad y el rendimiento de los nuevos procesos.Aun así, con la tolerancia EPE cada vez más pequeña en los nodos de 3NM y 2NM, los enfoques como FAV probablemente se volverán más convincentes.

Higo.2: Se utilizó un proceso de deposición selectiva para fabricar un nivel de dos niveles totalmente alineado a través de un nodo de 5 nm.Fuente: IBM/IITC

La deposición selectiva, también conocida como deposición selectiva del área (ASD), ha existido durante décadas, pero es solo en los últimos años que ha dado el paso de laboratorio a fabuloso. For ASD, the “killer app" proved to be deposition of cobalt caps on copper lines, which enables superior control of electromigration over traditional silicon nitride caps.Esa técnica fue adoptada por algunas compañías en el nodo de 10 nm.Junto con un revestimiento de cobalto debajo del cobre (los revestimientos también se llaman capas de nucleación o capas de pegamento porque permiten la adhesión de metal), el cobalto encierra el cobre en este esquema.

Los procesos ALD selectivos funcionan mejor cuando el objetivo es depositar metal en metal o dieléctrico en dieléctrico.Dependiendo del proveedor del equipo, se pueden usar diferentes mecanismos químicos para mantener la deposición selectiva y evitar la deposición donde no se desea.Para la metalización de contacto, la deposición selectiva de tungsteno potencialmente reduce la resistividad dramáticamente a través del llenado mejorado y potencialmente eliminando la barrera de estaño por completo (ver Higoura 3).Al eliminar las barreras y los revestimientos de la pared lateral, el tungsteno selectivo también permite una interfaz de metal a metal limpia para una menor resistencia general.Según los materiales aplicados, es posible una reducción del 40% en la resistencia.

Higo.3: El relleno selectivo de tungsteno de abajo hacia arriba proporciona una vía para eliminar las capas de barrera y revestimiento, mejorando el contacto y la resistencia.Fuente: Materiales aplicados

Cobalt and tungsten

Up until the 14nm or 10nm technology node, tungsten has remained the mainstay for making electrical contact to the metal/polysilicon gate and the source and drain silicide regions on transistors.En los últimos años, se adoptaron contactos de cobalto con una barrera delgada.Del mismo modo en líneas o vias, la barrera más delgada, junto con la ruta libre media más corta de cobalto (10 nm vs.39 nm para cobre), da como resultado una menor resistividad en cables pequeños (con una ruta de electrones más larga, la dispersión aumenta la resistencia neta).

Intel fue la primera compañía en usar Cobalt en producción a nivel de contacto, y de hecho, los problemas de integración con Cobalt pueden haber sido una causa parcial de problemas con los retrasos de 10 nm de Intel.No obstante, varios fabricantes de chips hicieron la transición al uso de cobalto en los procesos de producción para contactos, pero también como un revestimiento y material de limitación en interconexiones de cobre.

El metal de revestimiento afecta críticamente la calidad del relleno del cobre en líneas de interconexión a escala.En una presentación invitada en IITC, IBM demostró un rendimiento de electromigración mejorado utilizando un nuevo revestimiento, Rutenio dopado con cobalto por CVD [3], en relación con CVD Cobalt y CVD Rutenium en estructuras de metal de 36 nm.IBM determinó que el nuevo revestimiento brinda una mejor resistencia EM porque el cobalto en el revestimiento de rutenio suprime la difusión a lo largo de los límites de grano causados por la tapa de cobalto en cobre.El cobre de PVD con reflujo a bajas temperaturas (250 ° C) se está convirtiendo en la corriente principal para las interconexiones densas, mientras que el cobre electroales o el ECD se usan a nivel global.

The next metal: Ru or Mo?

It appears that at the 1nm node (20nm metal pitch), a change from copper to an alternative metal —ruthenium or molybdenum — will become necessary, at least for some levels.Curiosamente, tanto el molibdeno como el rutenio se están explorando como reemplazos de la línea de palabras para tungsteno en transistores de flash 3D NAND.

Para la elección de la industria para reemplazar el cobre, la resistencia a las características escaladas es la métrica Paramount.También es crítica es la resistencia EM, que está vinculada a la confiabilidad a largo plazo..Gran parte de la ventaja de Ruthenium, Molibdeno y Cobalt, es el potencial de eliminar los revestimientos, que ofrece más trinchera o por volumen para estar ocupada por el metal principal.El recocido de reflujo o láser puede usarse para maximizar el tamaño del grano.

"Para las líneas de metal, el rutenio es un reemplazo probable. While the bulk resistivity of ruthenium is 7 µohm-cm, the effective resistivity of a 20nm ruthenium film deposited with traditional sputtering is >11 µohm-cm," said Veeco’s Paranjpe.“Por lo tanto, se están explorando métodos alternativos como la deposición del haz de iones, que ofrecen un mayor control sobre la textura cristalina y el tamaño del grano.."

El rutenio es atractivo como una interconexión de próxima generación debido a su baja resistividad, alto punto de fusión, resistencia al ataque de los ácidos y un potencial extremadamente bajo de corrosión.

Los precursores de molibdeno, en contraste, son un orden de magnitud menos costoso que Rutenium.Es probable que no se necesite antes del nodo de 2 nm.

“Molybdenum is definitely cheaper, so if you’re a fab manager you will be happier," said Imec’s Tokei."Pero si usted es ingeniero, debe tener todos los datos disponibles para tomar una decisión entre los materiales, y aún no tenemos un conjunto de datos completo.."

Higo.4: Al construir un riel de la región de aislamiento del transistor a través de la oblea de silicio, la entrega de energía del transistor (trasera) se separa de la entrega de la señal (delantera).Fuente: IMEC

Buried power rails

The combination of BPR and backside power distribution (BPD) essentially takes power and ground wires, which previously were routed through the entire multi-level metal interconnect, and gives these a dedicated network on the wafer backside (see figure 4).Esto reduce la caída de voltaje (IR).

“En la interconexión convencional, debe optimizar en el metal 0 y el metal 1 para la potencia y las señales, por lo que la potencia impulsa una interconexión alta y la señal impulsa una interconexión delgada. You end up with a tradeoff, which is not optimal for either," explained Tokei."Al enrutar la potencia hacia la parte trasera, habrá interconexiones altas y relativamente amplias allí, y te queda con señal y reloj en la parte delantera con líneas relativamente flacas y resistentes, y obtienes significativamente la capacidad de ruta de ruta." He noted that thermal management is being evaluated carefully for these new structures.

Existen muchos desafíos con respecto a BPRS y BPD, incluyendo cómo construir el riel de energía enterrado, cómo conectar la red de distribución de energía al riel de potencia y cómo transferir la energía del riel de energía al transistor.Estas decisiones determinarán los esquemas de integración y las ganancias finales de potencia y escala.

Mehul Naik, Director Gerente de Desarrollo de Tecnología de Productos Avanzados en Materiales Aplicados, dijo que los desafíos de fabricación variarán, dependiendo del esquema, y pueden incluir llenados de metal de alta relaciónentre otros.

Intel anunció que utilizará su Powervia en su generación de 20å (2 nm), que su objetivo es tener en la producción de alto volumen en 2024.La ingeniería de semiconductores discutió PowerVia con Ann Kelleher de Intel, vicepresidenta senior y gerente general de desarrollo tecnológico, y preguntó cómo difería de otros enfoques en desarrollo. “Buried power rail, at the highest level, is the same general theme," Kelleher said."Sin embargo, difiere en cómo se logra.Estamos entregando el poder desde la parte posterior de la oblea al transistor.Básicamente, el riel de potencia enterrado lo está obteniendo desde el lado, por lo que tiene una arquitectura diferente para lograrlo.Es la diferencia clave."

En particular, el Powervia de Intel parece conectarse en los contactos, mientras que el riel de potencia de IMEC está integrado en la ITS (aislamiento de la zanja poco profunda).

David Fried, vicepresidente de productos computacionales en Lam Research, compara el enfoque de ferrocarril de energía enterrado en un sótano en una casa. “If you use a basement analogy, there will need to be a stairwell on each side," he said.“Ahora tiene la capacidad de acceder a los elementos en la planta baja desde ambos lados en lugar de solo uno.Esto puede abrir una dimensión de diseño completamente nueva cuando puede acceder a los transistores desde abajo o desde arriba.Es un gran cambio."

Si bien este cambio a la construcción de acceso a transistores en el frente de la oblea y traseros requerirá muchas innovaciones de procesos y diseño, el hecho de que la potencia trasera aún tenga una construcción plana de nivel por nivel se basa en los conocimientos existentes de la industria.

“This is one of the technologies I’m fairly optimistic about," said Fried."Son las innovaciones las que son difíciles y multifacéticas, pero en el fondo están probados.Entonces, un riel de potencia enterrado es solo otro nivel bidimensional en un flujo tridimensional.Todavía es un procesamiento plano, por lo que tiene una similitud con todo lo que ya hacemos.Ponerlo y hacer que funcione es muy, muy difícil, pero en esencia no es tan revolucionario como otras opciones."

Se requerirán innovaciones de procesos en metalización, dieléctricos y CMP. “When you take the power rail and connect it to the device, how do you make sure the interfaces are clean enough and how do you reduce power losses in that transfer? Pre-clean and integration with void-free low-resistivity metals will be very important," Applied Materials’ Naik said.“Se requerirán dieléctricos de presupuesto térmico de alta calidad (≤400 ° C), ya que estos procesos ocurren después de que se ha fabricado la metalización del lado delantero, incluida la metalización.."

Otra clave es CMP.Para el adelgazamiento de la oblea, la molienda de la oblea trasera será seguida por CMP para adelgazar la oblea del dispositivo. “From a yield perspective, it will be CMP’s job to make sure all incoming non-uniformity is managed to achieve the desired global wafer thickness uniformity at low defectivity," said Naik.

Desde el punto de vista del adelgazamiento de la oblea, tanto el apilamiento de múltiples chips para la memoria HBM como ahora la entrega de potencia trasera para la lógica, el adelgazamiento hasta 10 micras, pero hay un tremendo interés en ser más delgado.“El apilamiento de alta densidad está impulsando esta necesidad y los diseñadores quieren un silicio incluso más delgado que lo que está disponible hoy en día. From the moment something is needed, then technologists will extend the capability and that’s what is happening with chip stacking," said Tokei.

Conclusion

Chipmakers are evaluating many process changes for 5nm and beyond, including via resistance optimization, fully aligned vias, cobalt caps and contacts, and the separating of power and signal lines to free up congested interconnect layers.La industria de los semiconductores siempre está más abierta a realizar modificaciones graduales de procesos, en lugar de grandes cambios materiales y estructurales, siempre que sea posible..

Los nuevos revestimientos que mejoran la confiabilidad, eliminando la barrera de vía de fondo y VIA totalmente alineados, parecen estar habilitando soluciones.Los ingenieros están comenzando a resolver los desafíos en torno a los rieles de energía y el procesamiento trasero.La deposición selectiva ha ingresado a FABS para los límites de cobalto y probablemente obtendrá aceptación en aplicaciones adicionales en el futuro.

Referencias

Related Stories

Inside Intel’s Ambitious Roadmap

Five process nodes in four years, high-NA EUV, 3D-ICs, chiplets, hybrid bonding, and more.

Breaking the 2nm Barrier

New interconnects and processes will be required to reach the next process nodes.