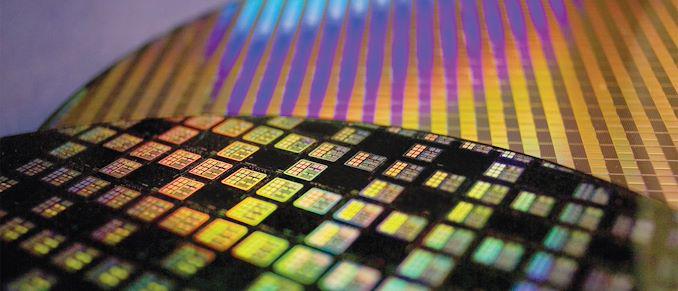

Taiwan Semiconductor Manufacturing Co. a des plans solides pour les prochaines années, mais les cycles de conception de la technologie de fabrication de la fonderie s'allongent. Par conséquent, pour répondre à tous les besoins de ses clients, l'entreprise devra continuer à offrir des versions demi-nœuds, améliorées et spécialisées de ses procédés de fabrication.

Le succès de TSMC au cours des 20 dernières années a été largement conditionné par la capacité de l'entreprise à proposer chaque année une nouvelle technologie de fabrication avec des améliorations PPA (puissance, performances, surface) et à introduire un tout nouveau nœud tous les 18 à 24 mois, tandis que maintenir des rendements élevés prévisibles. Mais à mesure que la complexité des processus de fabrication modernes atteint des niveaux sans précédent, il devient de plus en plus difficile de suivre le rythme de l'innovation tout en maintenant des rendements prévisibles et des principes de conception simples.

Avec le nœud N3 de TSMC, l'écart entre la montée en puissance N5 (classe 5 nm) et la montée en puissance N3 (classe 3 nm) passera à environ 2,5 ans, ce qui pourrait poser des problèmes au principal client de la fonderie, Apple. La bonne nouvelle est que le suivi de N3, N3E, semble arriver plus tôt que prévu. Pendant ce temps, avec N2, la cadence devrait s'étendre à environ trois ans, ce qui signifie en grande partie un changement stratégique dans la stratégie de développement de nœuds de TSMC.

N3E : un nœud amélioré de 3 nm inséré (presque)

Le N3 de TSMC est configuré pour apporter des améliorations complètes du nœud par rapport au N5, ce qui inclut 10 % à 15 % de performances en plus, 25 % à 30 % de puissance réduction et une densité de transistor jusqu'à 1,7 fois plus élevée pour la logique. Pour ce faire, il utilisera plus de 14 couches de lithographie dans l'ultraviolet extrême (EUV) (N5 en utilise jusqu'à 14, et N3 devrait en utiliser encore plus) et introduira certaines nouvelles règles de conception pour les couches de lithographie dans l'ultraviolet profond (DUV).

| Améliorations PPA annoncées des nouvelles technologies de processus Données annoncées lors des conférences téléphoniques, des événements, des points de presse et des communiqués de presse | |||||||

| TSMC | |||||||

| N7 vs 16FF+ | N7 vs< br>N10 | N7P contre N7 | N7+ contre N7 | N5 contre N7 | N5P vs N5 | N3 vs N5 | |

| Puissance | -60 % | -10 % | -15 % | -30 % | < td>-10 %-25-30 % | ||

| Performances | +30 % | ? | +7 % | +10 % | +15 % | +5 % | +10- 15 % |

| Zone logique % de réduction (Densité) | 70 % | > 37 % | - | ~17 % | 0,55x -45 % (1,8x) | - | 0,58x -42 % (1,7x) |

| Volume Fabrication | T2 2019 | T2 2020 | 2021 | < td>H2 2022

TSMC est sur le point de commencer à accélérer la production de puces à l'aide de son nœud N3 au cours du second semestre de l'année et livrera le premier commercial lot à un client (ou des clients) au début de 2023, date à laquelle il recevra les premiers revenus N3.

Alors que la technologie de processus N3 de TSMC a été conçue à la fois pour le calcul haute performance (qui est un terme que TSMC utilise pour décrire des applications telles que les processeurs, les GPU, les FPGA, les ASIC, etc.) et les smartphones, il est prouvé que le nœud a une fenêtre de processus plutôt étroite, ce qui rendrait difficile pour les développeurs de puces d'atteindre les spécifications souhaitées. C'est un problème car cela augmente le délai de rendement et réduit finalement les marges. Dans une tentative apparente de résoudre le problème, TSMC a développé la version N3E de la technologie qui élargit la fenêtre de processus et apporte des améliorations par rapport à N5.

"N3E étendra encore notre famille N3 avec des performances, une puissance et un rendement améliorés", a déclaré C. C. Wei, directeur général de TSMC.

À l'origine, TSMC prévoyait de commencer la fabrication à haut volume (HVM) en utilisant N3E environ un an après N3 (c'est-à-dire au troisième trimestre 2023), mais au cours des derniers mois, une rumeur a émergé selon laquelle TSMC intégrait HVM de N3E d'environ un trimestre en raison de tests de production meilleurs que prévu. Lors de sa dernière conférence téléphonique, TSMC a confirmé que les progrès de N3E étaient en avance sur le calendrier et qu'il envisageait de lancer une production de masse à l'aide de cette technologie, mais n'a pas précisé les plans exacts.

"Notre résultat N3E est assez bon", a déclaré le responsable de TSMC. "Les progrès sont en avance sur notre calendrier. Et le pull-in, oui, nous y réfléchissons. Jusqu'à présent, je n'avais toujours pas de données très solides à partager avec vous sur le nombre de mois que nous pouvons tirer. Mais oui, il est dans notre plan."

Gardant à l'esprit que les développeurs de puces ont leurs propres calendriers pour leurs conceptions, il est peu probable que tous puissent profiter de la rampe N3E antérieure, car leurs puces doivent également passer toutes les itérations de pré-production. Néanmoins, les progrès du N3E meilleurs que prévu sont un bon signe en général, surtout compte tenu du fait que la famille N3 de TSMC devra servir l'industrie pendant assez longtemps.

N2 : Attendez-vous aux premières puces en 2026

En fait, N3 et ses itérations évolutives resteront les offres de pointe de TSMC jusqu'à la fin de 2025, car le calendrier N2 (classe 2 nm) de la société semble assez conservateur.

Lorsque TSMC a parlé pour la première fois de son N2 en août 2020, il n'a pas révélé beaucoup de détails sur la technologie (nous savons maintenant qu'il adopte une structure de transistor gate-all-around [GAA]) ou sur son calendrier, mais a indiqué qu'il construirait une toute nouvelle usine près de Baoshan, dans le comté de Hsinchu, à Taïwan, pour ce nœud (certaines sources appellent cette nouvelle usine Fab 20). Les autorités taïwanaises ont approuvé le plan de construction à la mi-2021 et ce plan prévoyait le début de 2022 (plus tôt cette année, le conseil d'administration de TSMC a en effet accepté des crédits de capital pour une nouvelle construction de fab), nous pensons donc que la coque est en cours de construction au moment où nous parlons .

La construction de la coque prend généralement un an ou un peu plus, puis l'installation de l'équipement prend également plus d'un an. Nous prévoyons donc que la première phase de Fab 20 sera prête d'ici la mi-2024 au plus tard. TSMC prévoit de commencer la production à risque en utilisant sa technologie N2 à la fin de 2024, puis de lancer HVM vers la fin de 2025, ce qui signifie que l'écart entre la rampe N3 initiale au T3 2022 et la rampe N2 initiale au T4 2025 sera d'environ trois ans.

" Nos progrès jusqu'à présent aujourd'hui pour la N2 sont sur la bonne voie", a déclaré M. Wei. "Tout ce que je veux dire, c'est que oui, à la fin de 2024, [N2] entrera dans la production à risque. 2025, il sera en production, probablement vers la seconde moitié ou la - ou la fin de 2025. C'est notre emploi du temps."

Compte tenu de la durée des cycles de production de puces modernes, il est prudent de dire que les premières puces N2 fabriquées par TSMC arriveront dans les appareils grand public au plus tôt au début de 2026.

| Introduction du nouveau nœud de TSMC au cours des dernières années | |||||||

| N7 | N7P< /td> | N5 | N5P | N3 | N3E | N2 | |

| Type de transistor | FinFET | FinFET | FinFET | FinFET | FinFET | < td>FinFETGAA FET | |

| Risque de production | ? | ? | ? | ? | 2021 | 2022 | Fin 2024 |

| Volume Fabrication | T2 2018 | T2 2019 | T2 2020 | T2 2021 | T3 2022 | T2/T3 2023 | Fin 2025 |

Mais peut-être que les révélations publiques de TSMC sur N2 et Fab 20 sont trop conservateurs. Les analystes de China Renaissance Securities semblent être plus optimistes quant à l'état de préparation de Fab 20 que ne l'est TSMC, ce qui peut être un indicateur que la fonderie pourrait tirer N2 HVM d'un quart ou même de deux si le processus de fabrication répond ses objectifs de performance, de puissance et de rendement.

"Nous voyons également plus de clarté sur le calendrier d'expansion N2 de TSMC dans Fab 20 (Hsinchu)", a écrit Sze Ho Ng, analyste chez China Renaissance Securities, dans un rapport destiné aux clients. "Le déménagement de l'outil devrait commencer d'ici la fin de 2022, sur la base des plans de l'entreprise, avant la production de risques fin 2024E avec Intel (les" tuiles "graphiques du PC client Lunar Lake, tandis que les" tuiles "du processeur sont fabriquées à l'aide du 18A d'Intel) et Apple étant les principaux clients pour le support de capacité dédié. »

En attendant, insérer un nœud du quatrième trimestre 2025 au troisième trimestre 2025 alors que les clients alpha ont déjà défini leurs plans pour 2025 n'a peut-être pas beaucoup de sens, mais nous verrons certainement comment les choses se passeront avec N2.

Plus d'itérations N3

Cette année, les clients de TSMC qui ont besoin d'un processus de fabrication de pointe utiliseront la technologie N4 de l'entreprise, qui appartient à la famille N5 (avec N5, N5P, N4P et N4X ). Essentiellement, cela signifie qu'un nœud N5 restera l'offre la plus avancée de TSMC pendant trois années consécutives.

Les nœuds N3 devront également servir les clients de TSMC pendant encore trois ans (2023, 2024, 2025), nous allons donc pour voir plusieurs itérations de ce processus. Jusqu'à présent, TSMC a officiellement confirmé N3E et N3X (qui est une autre technologie de fabrication axée sur les performances semblable à N4X destinée principalement aux processeurs et aux ASIC de centre de données), mais je m'attendrais à ce que davantage de nœuds dérivés de N3 viennent traiter les SoC grand public en 2024 ~ 2025 .

Gardant à l'esprit que le N3 basé sur FinFET de TSMC devra rester compétitif par rapport aux 3GAP et 2GAE/2GAP de Samsung basés sur GAA en 2023 ~ 2025 et le 20A d'Intel (RibbonFET + PowerVia) en 2024 et 18A (High-NA EUV) en 2025, les ingénieurs de TSMC devront être assez créatifs avec leurs améliorations N3.

Du côté de la fonderie, TSMC restera en avance sur ses rivaux pendant un bon moment puisqu'Intel ne devrait pas investir de manière significative dans sa capacité dédiée IFS avant 2025 (donc ses capacités 20A et 18A pour les clients IFS seront probablement limité), tandis que Samsung Foundry est traditionnellement derrière TSMC en matière de capacité de pointe et préfère donner la priorité à sa société mère et à ses clients stratégiques (par exemple, Qualcomm). Mais le leadership formel de la technologie des processus est ce que les ingénieurs de TSMC devront maintenir avec N3 et ce sera difficile à faire compte tenu de l'agressivité d'Intel et de Samsung.

Des changements arrivent

De toute évidence, le tout nouveau processus de développement et la cadence d'accélération de TSMC sont passés à deux ans et demi avec N3 et passeront à trois ans avec N2, ce qui peut être considéré comme un ralentissement majeur par ses principaux clients. Pendant ce temps, l'attraction potentielle de N3E est un bon signe qui montre que l'entreprise peut faire ses progrès intra-nœuds assez rapidement. Par conséquent, la principale question est de savoir quelle sera l'importance des progrès intra-nœuds de TSMC à l'avenir. C'est une question à laquelle seul le temps répondra.

En attendant, il semble qu'avec le cycle de développement de nouveaux nœuds sur trois ans de TSMC, les futures avancées intra-nœuds seront beaucoup plus importantes pour l'entreprise et ses clients qu'elles ne le sont aujourd'hui.