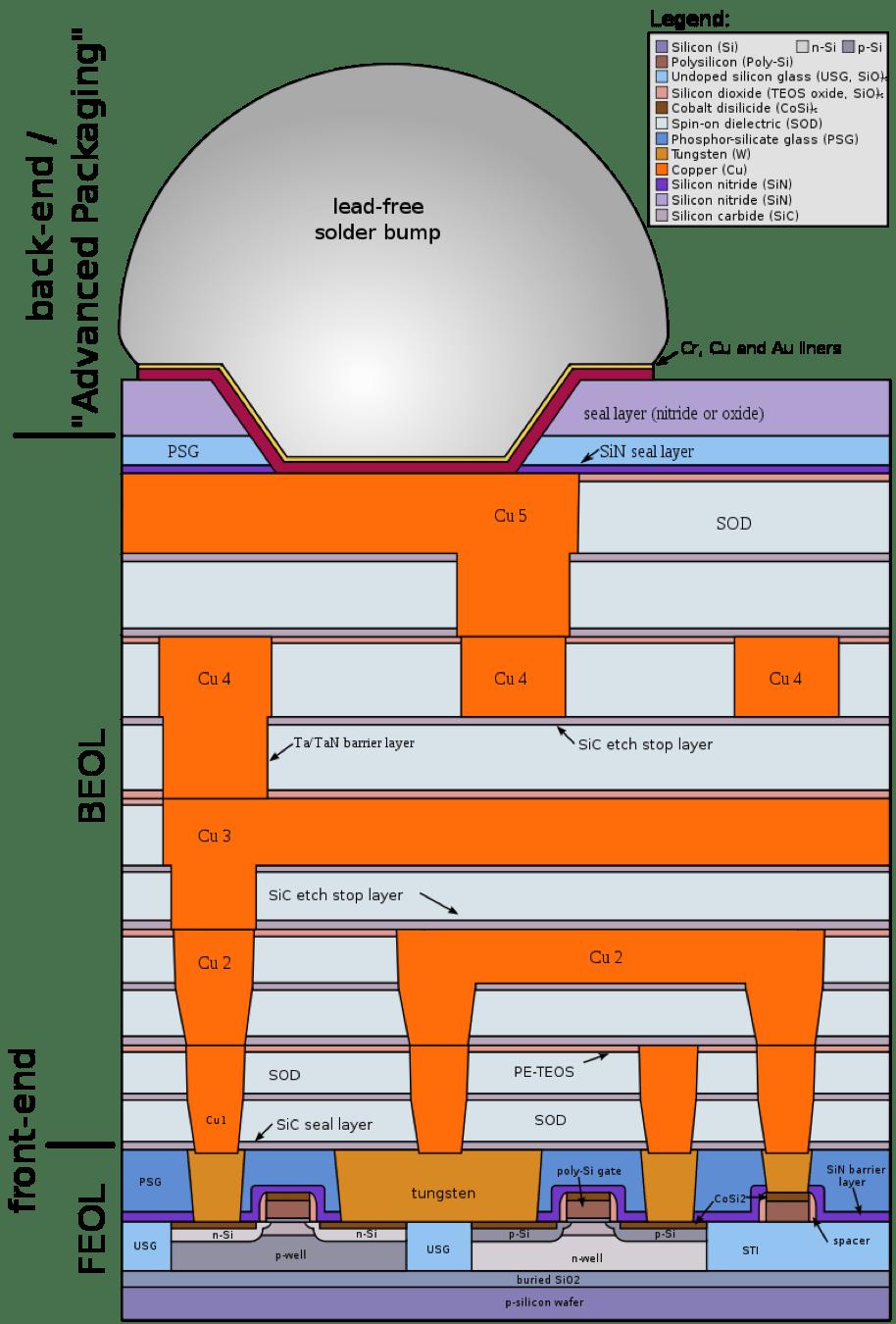

O escalamento do transistor está atingindo um ponto de inflexão a 3Nm, onde os Fets de nanofeetes provavelmente substituirão os FINFETs para atender às metas de desempenho, energia, área e custo (PPAC).Uma mudança arquitetônica significativa está sendo avaliada da mesma forma para interconexões de cobre a 2 nm, um movimento que reconfiguraria a maneira como a energia é entregue aos transistores.

Essa abordagem depende dos chamados trilhos de energia enterrados (BPRs) e distribuição de energia traseira, deixando as interconexões do lado da frente para transportar sinais.A Intel anunciou que usará sua estrutura Powervia em sua geração 20å (2NM equivalente) e outros fabricantes de chips estão avaliando esquemas semelhantes.

Os fabricantes de chips também provavelmente substituirão o cobre em alguns níveis por rutênio ou molibdênio assim que o nó de 2nm.Outras alterações mais modestas estenderão as interconexões de Damasceno de cobre usando baixa resistência por meio de processos, forros alternativos e totalmente alinhados por meio de abordagens.

Grande parte da otimização acontece em torno dos links fracos da corrente - o contato (metal 0), metal 1 e vias, onde os atrasos de RC têm maior probabilidade de diminuir o chip."Para preenchimento, deposição conforme de barreira, sementes e via metal pode ser suplantada por deposição sem barreira e preenchimento de cobalto de baixo para cima, e talvez até rutênio", disse Ajit Paranjpe, CTO da Veeco.

Os desafios de interconexão começam na litografia, onde o EUV é empregado em todo o processo de 5 nm, contribuindo significativamente para o custo.

EUV and BEOL patterning

Only a handful of mask levels require EUV lithography at the 7nm node, but this changes to between 15 and 18 levels at 5nm (about 30nm metal pitch).Na litografia, uma preocupação crescente são os erros de colocação de arestas (EPES) devido a recursos imprecisivamente alinhados.Robert Socha, um companheiro de ASML, enfatizou a necessidade de controlar e reduzir os colaboradores da EPES no nó de 5 nm.Um colaborador crítico é erros de sobreposição, com orçamento de sobreposição de apenas 2.5nm (5 átomos de silício de largura) no nó de 5 nm.

"Vimos o elemento de sobreposição do orçamento da EPE, encolhendo o mais rápido com maior variação no campo", disse Andrew Cross, diretor de soluções de controle de processos da KLA.“Isso leva a uma amostragem de sobreposição óptica mais alta, técnicas de medição de sobreposição aprimoradas e uso de medições de sobreposição baseadas em SEM após resistir ao desenvolvimento e após a gravação, o que exige sinergia entre as ferramentas ópticas e baseadas em vigas eletrônicas.”

Via optimization

A key strategy in extending copper technology involves eliminating the barrier metal, TaN, at the copper via bottom.Uma maneira de isso ser realizado é depositar um filme de monocamada auto-montada (SAM) seletivamente, depositar o bronzeado pela deposição de camada atômica (ALD) ao longo das paredes laterais e, finalmente, removendo o SAM e enchendo com cobre.Na IITC, a Tel descreveu esse processo usando dupla integração de Damascene [1] e comparando duas monocamadas auto-montadas (A e B).Seguindo a barreira tan Ald, os SAMs foram evaporados, seguidos pela deposição de eletrólito de cobre (ELD) na VIA (veja a Figooooura 1).Depois da VIA pré -enchimento, um revestimento de rutênio foi depositado por CVD nas paredes laterais da trincheira, seguido de preenchimento de PVD ionizado de cobre.Com Sam B, os resultados não mostraram TA (EDX) no Via Bottom.Um aspecto essencial de qualquer SAM é que ele pode suportar a temperatura do processo de ALD, que é de cerca de 350 ° C.

Os fabricantes de chips estão cada vez mais procurando processos SAM, seja por CVD ou spin-coat, como crítico para reduzir a resistência geral e estender os processos de Damasceno de cobre ao nó de 2nm.

Outra estratégia que reduz o volume de metal de barreira (Tan) no Via Bottom envolve uma transição de PVD Tan para Ald Tan, que é mais conforme e resulta em um filme mais fino e contínuo.Espera -se que Ald Tan seja amplamente implementado no nó de 5 nm, talvez com os processos SAM.

Figoooo.1: Neste processo de monocamada auto-montada (SAM), um filme mascara o Via Bottom durante o ALD da barreira e sementes de cobre.O SAM é então removido por vaporização a 325 ° C, seguido de preenchimento de cobre.Fonte: Tel/IITC

Fully aligned vias, selective deposition

The idea behind fully aligned vias (FAVs) is to reduce the impact of edge placement errors between vias and lines, which lead to device failures and long-term reliability issues.Desde o nó de 32 nm, os fabricantes de chips estão empregando métodos auto-alinhados usando máscaras duras de lata para alinhar interconexões ao nível abaixo.Em vias totalmente alinhadas, a via abaixo e acima é registrada.Existem dois métodos para alcançar favs, gravando um pouco de cobre das linhas abaixo e depois padronizando e depositando a VIA, ou depositando um filme dielétrico seletivamente no dielétrico baixo, seguido de via padrão.

Os engenheiros da IBM e LAM Research apresentaram uma abordagem totalmente alinhada usa deposição dielétrica seletiva em um processo geral simplificado [2].De acordo com o grupo, a integração favorita pode permitir 70% de menor resistência e um aumento de 30% na área de contato, mantendo a confiabilidade via linha (consulte a Figoooura 2).Utilizando estruturas de teste de 32nm-pitch de cobre e baixo k dielétrico (SICOH), a equipe usou uma química úmida para receber o cobre, o revestimento e a barreira.

“[A Etch de recesso], quando combinada com uma tampa dielétrica seletiva e seletiva, atua como um padrão de orientação, mitigação de sobreposição e dimensão crítica (CD)..Um filme seletivo de óxido de alumínio foi depositado pela CVD no Low-K e atua como uma parada parcial.A chave para o sucesso do processo é a alta seletividade com o crescimento lateral limitado do filme dielétrico, e nenhuma diminuição ou variação de resistência em comparação com seu processo FAV padrão.A IBM afirmou que uma vantagem adicional é a menor proporção das linhas de metal (porque o recesso é raso), o que facilita o enchimento de cobre.

Neste momento, não está claro o quão popular totalmente alinhada por meio de abordagens se tornará."A questão é de que forma - em que níveis e em que tom (vias totalmente alinhados) serão necessários?"pergunta Zsolt Tekei, um companheiro de IMEC.Ele observou que, embora as abordagens de gravação e deposição seletiva tenham seus prós e contras, a questão principal é a defeito e aumentar o rendimento em novos processos.Mesmo assim, com a tolerância EVEs e sempre pequena nos nós de 3 nm e 2nm, abordagens como Fav provavelmente se tornarão mais atraentes.

Figoooo.2: Um processo de deposição seletiva foi usado para fabricar um nó de dois níveis totalmente alinhado por um nó de 5 nm.Fonte: IBM/IITC

A deposição seletiva, também conhecida como deposição seletiva de área (TEA), existe há décadas, mas é apenas nos últimos anos que deu o passo do laboratório para o FAB.Para TEA, o “aplicativo assassino” provou ser deposição de tampas de cobalto nas linhas de cobre, o que permite o controle superior da eletromigração sobre as tampas tradicionais de nitreto de silício.Essa técnica foi adotada por algumas empresas no nó de 10 nm.Juntamente com um revestimento de cobalto embaixo do cobre (os revestimentos também são chamados de camadas de nucleação ou cola porque permitem a adesão metálica), o cobalto envolve o cobre neste esquema.

Os processos seletivos de ALD têm melhor desempenho quando o objetivo é depositar metal em metal ou dielétrico em dielétrico.Dependendo do fornecedor do equipamento, diferentes mecanismos químicos podem ser usados para manter a deposição seletiva e impedir a deposição onde não é procurado.Para metalização de contato, a deposição seletiva de tungstênio reduz potencialmente a resistividade dramaticamente através do enchimento aprimorado e potencialmente eliminando completamente a barreira de lata (veja a Figooura 3).Ao eliminar barreiras e revestimentos da parede lateral, o tungstênio seletivo também permite uma interface metal para metal limpa para menor resistência geral.De acordo com os materiais aplicados, é possível uma redução de 40% na resistência.

Figoooo.3: O preenchimento de baixo para cima do tungstênio seletivo fornece um caminho para eliminar as camadas de barreira e revestimento, melhorando o contato e a resistência.Fonte: Materiais Aplicados

Cobalt and tungsten

Up until the 14nm or 10nm technology node, tungsten has remained the mainstay for making electrical contact to the metal/polysilicon gate and the source and drain silicide regions on transistors.Nos últimos anos, contatos de cobalto foram adotados com uma fina barreira de lata.Da mesma forma em linhas ou vias, a barreira mais fina, juntamente com o caminho livre médio mais curto do cobalto (10nm vs.39 nm para cobre), resulta em menor resistividade em fios pequenos (com caminho mais longo, a dispersão aumenta a resistência líquida).

A Intel foi a primeira empresa a usar o cobalto na produção no nível de contato e, de fato, os problemas de integração com o cobalto podem ter sido uma causa parcial de problemas com os atrasos de 10 nm da Intel.No entanto, vários fabricantes de chips fizeram a transição para o uso de cobalto em processos de produção para contatos, mas também como revestimento e material de limite em interconexões de cobre.

O metal do revestimento afeta criticamente a qualidade de preenchimento do cobre em linhas de interconexão em escala.Em uma apresentação convidada no IITC, a IBM demonstrou melhor desempenho de eletromigração usando um novo forro, rutênio dopado com cobalto por CVD [3], em relação aos revestimentos de cobalto CVD e CVD Ruthenium em estruturas metálicas de 36nm.A IBM determinou que o novo revestimento oferece melhor resistência em EM porque o cobalto no revestimento de rutênio suprime a difusão ao longo dos limites dos grãos causados pela tampa de cobalto em cobre.O cobre do PVD com reflexão a baixas temperaturas (250 ° C) está se tornando mainstream para interconexões densas, enquanto o cobre ou o ECD eletrolles são usados em níveis globais.

The next metal: Ru or Mo?

It appears that at the 1nm node (20nm metal pitch), a change from copper to an alternative metal —ruthenium or molybdenum — will become necessary, at least for some levels.É interessante.

Para a escolha do setor de substituir o cobre, a resistência em recursos em escala é a métrica Paramount.Também crítico é a resistência em EM, que está ligada à confiabilidade de longo prazo.Grande parte da vantagem do rutênio, molibdênio e cobalto, é o potencial de eliminar revestimentos, proporcionando mais trincheiras ou por volume a ser ocupado pelo metal principal.O recozimento de refluxo ou laser pode ser usado para maximizar o tamanho de grão.

“Para linhas de metal, o rutênio é um substituto provável. While the bulk resistivity of ruthenium is 7 µohm-cm, the effective resistivity of a 20nm ruthenium film deposited with traditional sputtering is >11 µohm-cm,” said Veeco’s Paranjpe.“Assim, métodos alternativos, como a deposição de feixe de íons, que oferecem maior controle sobre a textura cristalina e o tamanho dos grãos, estão sendo explorados.”

O rutênio é atraente como interconexão de próxima geração devido à sua baixa resistividade, alto ponto de fusão, resistência ao ataque de ácidos e potencial extremamente baixo para corrosão.

Os precursores de molibdênio, por outro lado, são uma ordem de magnitude mais barata que o rutênio.Nem provavelmente será necessário antes do nó de 2nm.

"O molibdênio é definitivamente mais barato, por isso, se você é um gerente fabuloso, ficará mais feliz", disse o IMEC's Tekei."Mas se você é um engenheiro, precisa ter todos os dados disponíveis para tomar uma decisão entre os materiais e ainda não temos um conjunto de dados completo.”

Figoooo.4: Ao construir um trilho a partir da região de isolamento do transistor através da bolacha de silício, a entrega de energia do transistor (parte traseira) é separada da entrega do sinal (frente).Fonte: IMEC

Buried power rails

The combination of BPR and backside power distribution (BPD) essentially takes power and ground wires, which previously were routed through the entire multi-level metal interconnect, and gives these a dedicated network on the wafer backside (see figure 4).Isso reduz a queda de tensão (IR).

“Na interconexão convencional, você deve otimizar o metal 0 e o metal 1 para energia e sinais, para que a energia acione uma interconexão alta e o sinal aciona uma interconexão magra.Você acaba com uma troca, o que não é ideal para também ”, explicou TeKei."Ao rotear o poder para a parte traseira, haverá interconexões altas e relativamente amplas lá, e você ficará com sinal e relógio na frente com linhas relativamente magras e resistivas, e você ganha significativamente a capacidade de rotas.Ele observou que o gerenciamento térmico está sendo avaliado cuidadosamente para essas novas estruturas.

Existem muitos desafios em relação aos BPRs e BPDs, incluindo como construir o trilho de energia enterrado, como conectar a rede de distribuição de energia ao trilho de energia e como transferir energia do trilho de energia para o transistor.Essas decisões determinarão os esquemas de integração e os ganhos finais de poder e escala.

Mehul Naik, diretor administrativo de desenvolvimento avançado de tecnologia de produtos da Applied Materials, disse que os desafios de fabricação variam, dependendo do esquema, e podem incluir preenchimentos de metal de alta proporção, opções de metal e dielétrico e diminuir a bolacha através da moagem traseira e CMP,entre outros.

A Intel anunciou que usará seu Powervia em sua geração 20å (2nm), que pretende ter na produção de alto volume em 2024.A Engenharia de Semicondutores discutiu Powervia com Ann Kelleher, vice -presidente sênior e gerente geral de desenvolvimento de tecnologia, e perguntou como ele diferiu de outras abordagens em desenvolvimento."O trilho de força enterrado, no mais alto nível, é o mesmo tema geral", disse Kelleher."No entanto, difere em como é alcançado.Estamos entregando o poder desde a parte de trás da bolacha para o transistor.O Rail de Power Enterrado está basicamente pegando -o de frente, então você tem uma arquitetura diferente para alcançar isso.É a diferença chave.”

Notavelmente, a Powervia da Intel parece se conectar nos contatos, enquanto o trilho de energia da IMEC está incorporado ao STI (isolamento raso da vala).

David Fried, vice -presidente de produtos computacionais da LAM Research, compara a abordagem do Rail Power enterrado de um porão em uma casa."Se você usar uma analogia do porão, precisará haver uma escada de cada lado", disse ele.“Agora você tem a capacidade de acessar os itens no térreo de ambos os lados, em vez de apenas um.Isso pode abrir uma nova dimensão de design quando você pode acessar os transistores por baixo ou de cima.É uma grande mudança.”

Embora essa mudança para a construção de acesso aos transistores na frente e traseira de bolacha exigirá muitas inovações de processo e design, o fato de que o poder de trás ainda terá a construção de nível a nível planar que se baseia no know-how da indústria existente.

"Esta é uma das tecnologias sobre a qual sou bastante otimista", disse Fried."São as inovações que são difíceis e multifacetadas, mas na sua essência são comprovadas.Portanto, um trilho de força enterrado é apenas mais um nível bidimensional em um fluxo tridimensional.Ainda é um processamento planar, por isso é similaridade com tudo o que já fazemos.Juntá -lo e fazê -lo funcionar é muito, muito difícil, mas em sua essência não é tão revolucionário quanto algumas outras opções.”

As inovações de processo em metalização, dielétrica e CMP serão necessárias.“Quando você pega o trilho de energia e o conecta ao dispositivo, como você garante que as interfaces estejam limpas o suficiente e como você reduz as perdas de energia nessa transferência?Pré-limpar e integração com os metais de baixa resistividade sem vazios serão muito importantes ”, disse Naik, 'Naik,' Naik, '.“Serão necessários dielétricos de alto orçamento térmico de alta qualidade (≤400 ° C), pois esses processos ocorrem após o dispositivo do lado frontal, incluindo metalização, foi fabricado.”

Outra chave é CMP.Para desbaste de wafer, a moagem de bolas traseira será seguida pelo CMP para diminuir a bolacha do dispositivo."De uma perspectiva de rendimento, será o trabalho da CMP garantir que toda a não uniformidade seja gerenciada para alcançar a uniformidade de espessura global de wafer desejada com baixa defeito", disse Naik.

Do ponto de vista do desbaste de wafer, o empilhamento multi-chip para a memória HBM e agora a entrega de energia na parte traseira para lógica, diminuindo o desbaste para 10 mícrons, mas há um tremendo interesse em ficar mais fino.“O empilhamento de alta densidade está impulsionando essa necessidade e os designers querem silício ainda mais fino do que o que está disponível hoje.Desde o momento em que algo é necessário, os tecnólogos estenderão a capacidade e é isso que está acontecendo com o empilhamento de chips ”, disse Tokei.

Conclusion

Chipmakers are evaluating many process changes for 5nm and beyond, including via resistance optimization, fully aligned vias, cobalt caps and contacts, and the separating of power and signal lines to free up congested interconnect layers.A indústria de semicondutores está sempre mais aberta a fazer modificações graduais de processo, em vez de grandes mudanças materiais e estruturais, sempre que possível.

Novos revestimentos que aumentam a confiabilidade, removendo a barreira de via fundo e vias totalmente alinhados, parecem estar habilitando soluções.Os engenheiros estão começando a resolver os desafios em torno dos trilhos de energia e processamento traseiro.A deposição seletiva entrou no Fabs para tampas de cobalto e provavelmente obterá aceitação em aplicações adicionais daqui para frente.

Referências

Related Stories

Inside Intel’s Ambitious Roadmap

Five process nodes in four years, high-NA EUV, 3D-ICs, chiplets, hybrid bonding, and more.

Breaking the 2nm Barrier

New interconnects and processes will be required to reach the next process nodes.